## CHAPTER

3

# ARM, MOTOROLA, AND INTEL INSTRUCTION SETS

## **CHAPTER OBJECTIVES**

In this chapter, which has three independent parts, you will learn about the following instruction set architectures:

- ARM (Part 1)

- Motorola 68000 (Part II)

- Intel IA-32 Pentium (Part III)

The basic ideas of instruction sets, addressing modes, and instruction execution were introduced in Chapter 2. Assembly language representation for machine instructions and programs was used to present a number of program examples. In this chapter, we study how these basic ideas have been implemented in ARM, Motorola 68000, and Intel IA-32 ISAs. The ARM instruction set exemplifies RISC design, and the 68000 and IA-32 instruction sets illustrate the CISC design style. The three parts of this chapter, one for each instruction set, are independent complete units. The generic programs presented in Chapter 2 are coded in each of the three instruction sets. It is important to have a good understanding of the full discussion of basic ideas and programs in Chapter 2 because the corresponding discussions here are more brief. Appendices B, C, and D give concise summaries of the three ISAs, and contain more detail than is provided here in Chapter 3.

# PART I THE ARM EXAMPLE

Advanced RISC Machines (ARM) Limited has designed a family of microprocessors, and it licenses the designs to other companies for chip fabrication and use in computer products and embedded systems. The ARM company is relatively new, having evolved out of the Acorn Computers company that developed processor designs in the early 1980s. The main use for ARM microprocessors is in low-power and low-cost embedded applications such as mobile telephones, communication modems, automotive engine management systems, and hand-held digital assistants [1]. The book by Furber [2] contains a wealth of information on ARM design and implementation; the Clements text [3] uses ARM as a major example, and the book by van Someren and Atack [4] describes assembly language programming for ARM. Detailed information is also available at the ARM web site [5]. All ARM processors share the same basic machine instruction set. The version used here is the one implemented by the ARM7 processor. Later versions added features that are not relevant for the level of discussion in this chapter. In Chapter 11, we describe some of the added features in these later versions of the architecture. The programs from Chapter 2 are presented here in the ARM assembly language in order to illustrate various aspects of the ARM architecture.

## 3.1 REGISTERS, MEMORY ACCESS, AND DATA TRANSFER

In the ARM architecture, memory is byte addressable, using 32-bit addresses, and the processor registers are 32 bits long. Two operand lengths are used in moving data between the memory and the processor registers: bytes (8 bits) and words (32 bits). Word addresses must be aligned, that is, they must be a multiple of 4. Both little-endian and big-endian memory addressing is supported. (See Section 2.2.2.) The choice is determined by an external input control line to the processor. When a byte is loaded from memory into a processor register or stored from a register into the memory, it is always located in the low-order byte position of the register.

Memory is accessed only by Load and Store instructions. All arithmetic and logic instructions operate only on data in processor registers. This arrangement is a basic

feature of RISC architectures. Its implications for simplicity of processor design and performance will be examined in Chapter 8.

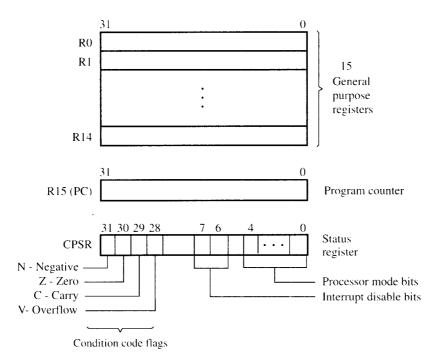

#### 3.1.1 REGISTER STRUCTURE

The processor registers used by application programs are shown in Figure 3.1. There are sixteen 32-bit registers labeled R0 through R15, which consist of fifteen general purpose registers (R0 through R14) and the Program Counter (PC) register, R15. The general purpose registers can hold either memory addresses or data operands. The Current Program Status Register (CPSR), or simply the Status register, holds the condition code flags (N, Z, C, V), interrupt disable flags, and processor mode bits. The information represented by the condition code flags is described in Section 2.4.6. The use of processor mode bits and interrupt disable bits will be described in conjunction with input/output operations and interrupts in Chapter 4. Here, we will assume that the processor is in User mode and is executing an application program.

There are 15 additional general-purpose registers called the *banked* registers. They are duplicates of some of the R0 to R14 registers. They are used when the processor switches into Supervisor or Interrupt modes of operation. Saved copies of the Status register are also available in these nonUser modes. These banked registers and Status register copies will also be discussed in Chapter 4.

Figure 3.1 ARM register structure.

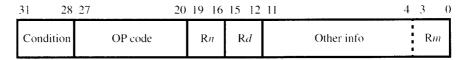

Figure 3.2 ARM instruction format.

#### 3.1.2 MEMORY ACCESS INSTRUCTIONS AND ADDRESSING MODES

Each instruction in the ARM architecture is encoded into a 32-bit word in a reasonably uniform way, typical of RISC designs. Access to memory is provided only by Load and Store instructions. The basic encoding format for these instructions, as well as for the Move, Arithmetic, and Logic instructions is shown in Figure 3.2. More detail is given in Appendix B. An instruction specifies a conditional execution code (Condition), the OP code, two or three registers (Rn, Rd, and Rm), and some other information. If register Rm is not needed, the "Other info" field extends to bit  $b_0$ . In a Load instruction, the operand is transferred from the memory into the general-purpose register named in the 4-bit Rd field. In a Store instruction, the operand is transferred from Rd into the memory. If the operand is a byte, it is always located in the low-order byte position of the register, and in a Load instruction, the high-order 24 bits of the register are filled with zeros.

#### **Conditional Execution of Instructions**

A distinctive and somewhat unusual feature of ARM processors is that all instructions are conditionally executed, depending on a condition specified in the instruction. The instruction is executed only if the current state of the processor condition code flags satisfies the condition specified in bits  $b_{31-28}$  of the instruction. Otherwise, the processor proceeds to the next instruction. One of the conditions is used to indicate that the instruction is always executed. The usefulness of conditional execution will be seen in the examples in Section 3.7. For now, we will ignore this feature and assume that the condition field of the instruction contains the "always executed" code.

#### **Memory Addressing Modes**

The basic method for addressing memory operands is to generate the effective address, EA, of the operand by adding a signed offset to the contents of a base register Rn, which is specified in the instruction as shown in Figure 3.2. The magnitude of the offset is either an immediate value, contained in the low-order 12 bits of the instruction, or it is the contents of a third register, Rm, named by the low-order four bits,  $b_{3-0}$ . The sign (direction) of the offset is contained in the OP-code field.

For example, the Load instruction

LDR

$$Rd$$

,  $[Rn$ , #offset]

specifies the offset (expressed as a signed number) in the immediate mode and performs the operation

$$Rd \leftarrow [[Rn] + offset]$$

Note that the destination register, Rd, is listed first. This is opposite to the order used in Chapter 2. The instruction

LDR

$$Rd$$

,  $[Rn.Rm]$

performs the operation

$$Rd \leftarrow [[Rn] + [Rm]]$$

Since the contents of Rm are the magnitude of the offset, Rm must be preceded by a minus sign if a negative offset is desired. In Chapter 2, these two addressing modes were defined as the Index and Base with index modes, respectively. An offset of zero does not have to be specified explicitly. Hence, the instruction

LDR

$$Rd$$

,[ $Rn$ ]

performs the operation

$$Rd \leftarrow [[Rn]]$$

using the addressing mode that was defined as the Indirect mode in Chapter 2.

The OP-code mnemonic LDR specifies that a 32-bit word is loaded from the memory into a register. A byte operand can be loaded into the low-order byte position of a register by using the mnemonic LDRB. The higher order bits are filled with zeros.

Store instructions have the mnemonics STR and STRB. For example, the instruction

STR

$$Rd$$

,[ $Rn$ ]

performs the operation

$$[Rn] \leftarrow [Rd]$$

transferring a word operand into the memory. The STRB instruction transfers the byte contained in the low-order end of Rd.

ARM documents refer to all of these modes, and others that we will describe shortly, as indexed addressing modes. The form that we have used in these first examples is called the Pre-indexed addressing mode because the effective address of the operand is generated by adding the offset to the contents of the base register Rn. The contents of register Rn are not changed. Addressing modes that are similar to the Autodecrement and Autoincrement modes that were discussed in Chapter 2 are also provided. They are called Pre-indexed with writeback and Post-indexed, respectively.

Definitions of all three modes are given as:

*Pre-indexed mode* — The effective address of the operand is the sum of the contents of the base register Rn and an offset value.

*Pre-indexed with writeback mode* — The effective address of the operand is generated in the same way as in the Pre-indexed mode, and then the effective address is written back into Rn.

*Post-indexed mode* — The effective address of the operand is the contents of Rn. The offset is then added to this address and the result is written back into Rn.

Table 3.1 specifies the assembly language syntax for these addressing modes, and

Table 3.1 ARM indexed addressing modes

| Name                                               | Assembler syntax          | Addressing function                                                    |

|----------------------------------------------------|---------------------------|------------------------------------------------------------------------|

| With immediate offset:                             |                           |                                                                        |

| Pre-indexed                                        | [Rn, #offset]             | EA = [Rn] + offset                                                     |

| Pre-indexed with writeback                         | [Rn, #offset]!            | EA = [Rn] + offset;<br>$Rn \leftarrow [Rn] + offset$                   |

| Post-indexed                                       | [Rn], #offset             | $EA = [Rn];$ $Rn \leftarrow [Rn] + offset$                             |

| With offset magnitude in Rm:                       |                           |                                                                        |

| Pre-indexed                                        | $[Rn, \pm Rm, shift]$     | $EA = [Rn] \pm [Rm]$ shifted                                           |

| Pre-indexed with writeback                         | $[Rn, \pm Rm, shift]!$    | $EA = [Rn] \pm [Rm]$ shifted;<br>$Rn \leftarrow [Rn] \pm [Rm]$ shifted |

| Post-indexed                                       | $[Rn]$ , $\pm Rm$ , shift | EA = $\{Rn\}$ ;<br>R $n \leftarrow [Rn] \pm [Rm]$ shifted              |

| Relative<br>(Pre-indexed with<br>immediate offset) | Location                  | EA = Location<br>= [PC] + offset                                       |

$\mathsf{EA} = \mathsf{effective} \; \mathsf{address}$

$\label{eq:offset} \text{offset} = \text{a signed number contained in the instruction}$

shift = direction #integer

where direction is LSL for left shift or LSR for right shift, and integer is a 5-bit unsigned number specifying the shift amount

$\pm Rm$  = the offset magnitude in register Rm can be added to or subtracted from the contents of base register Rm

gives expressions for the calculation of the effective address. EA, and the writeback operations. The exclamation mark signifies writeback in the Pre-indexed addressing mode. The Post-indexed mode always involves writeback, so the exclamation mark is not needed. Note that pre- and post-indexing are distinguished by the way the square brackets are used. When only the base register is enclosed in square brackets, its contents are used as the effective address. The offset is added to the register contents after the operand is accessed. In other words, post-indexing is specified. This is a generalized form of the Autoincrement addressing mode described in Section 2.5. When both the base register and the offset are placed inside the square brackets, the sum is used as the effective address of the operand, that is, pre-indexing is used. If writeback is to be performed, it must be indicated by the exclamation mark (!). Pre-indexing with writeback is a generalization of the Autodecrement addressing mode discussed in Section 2.5.

In all three addressing modes, the offset may be given as an immediate value in the range  $\pm 4095$ . Alternatively, the magnitude of the offset may be specified as the contents of the third register, Rm, with the sign (direction) of the offset specified by a  $\pm$  prefix on the register name. For example, the instruction

performs the operation

$$R0 \leftarrow [[R1] - [R2]]$$

The effective address of the operand, [R1] - [R2], is then loaded into R1 because writeback is specified by the exclamation mark.

When the offset is given in a register, it may be scaled by a power of 2 by shifting to the right or to the left. This is indicated in the assembly language by placing the shift direction, LSL for left shift or LSR for right shift, and the shift amount, after the register name Rm, as shown in Table 3.1. The amount of the shift is specified by an immediate value in the range 0 to 31. For example, the contents of R2 in the example above may be multiplied by 16 before being used as an offset as follows:

This instruction will perform the operation

$$R0 \leftarrow [[R1] - 16 \times [R2]]$$

and will then load the effective address into R1.

The Program Counter, PC, may be used as the Base register Rn. In this case, the Relative addressing mode, as described in Section 2.5, is implemented. The assembler determines the immediate offset as the signed distance between the address of the operand and the contents of the updated PC. When the effective address is calculated at instruction execution time, the contents of the PC will have been updated to the address two words (8 bytes) forward from the instruction containing the Relative addressing mode. The reason for this is related to pipelined execution of instructions, which will be discussed in Chapter 8.

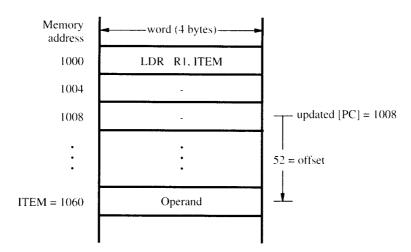

An example of the Relative mode is shown in Figure 3.3a. The address of the operand, given symbolically as ITEM in the instruction, is 1060. There is no Absolute addressing mode available in the ARM architecture. Therefore, when the address of an operand is given in this way in the assembly language, the assembler always uses the Relative addressing mode. This is implemented by the Pre-indexed mode with an immediate offset, using PC as the base register. As shown in the figure, the offset calculated by the assembler is 52 because the updated PC will contain 1008 when the offset is added to it during program execution, and the effective address to be generated is 1060 = 1008 + 52. The operand must be within the range of 4095 bytes forward or backward from the updated PC. If the operand address given in the instruction is outside this range, an error is indicated by the assembler and a different addressing mode must be used to access the operand.

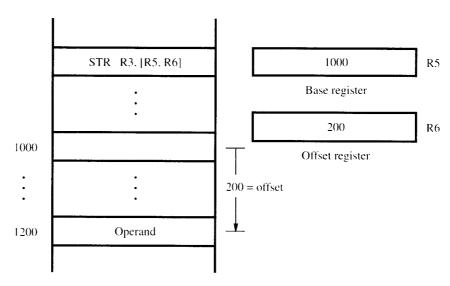

Figure 3.3b shows an example of the Pre-indexed mode with the offset contained in register R6 and the base value contained in R5. The Store instruction (STR) stores the contents of R3 into memory word location 1200.

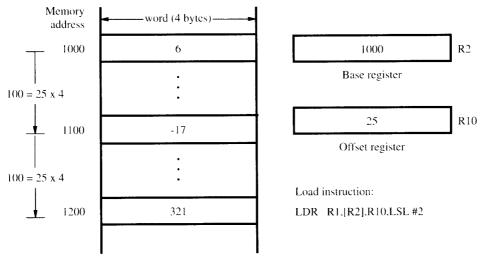

The examples shown in Figure 3.4 illustrate the usefulness of the writeback feature in the Post-indexed and Pre-indexed addressing modes. Figure 3.4a shows the first three numbers of a list of 25 numbers that are spaced 25 words apart, starting at memory address 1000. They comprise the first row of a 25  $\times$  25 matrix of numbers stored in column order. The first number of the first row of the matrix is stored in word location 1000. The numbers at addresses  $1100, 1200, \ldots, 3400$  are successive numbers of the

--

(a) Relative addressing mode

(b) Pre-indexed addressing mode

Figure 3.3 Examples of ARM memory addressing modes.

first row. The 25 memory locations 1000, 1004, 1008,  $\dots$ , 1096 contain the first column of the matrix.

Successive numbers in the first row of the matrix can be accessed conveniently using the Post-indexed addressing mode with writeback, with the offset contained in a register. Suppose that R2 is used as the base register and that it contains the initial address value 1000. Register R10 is used to hold the offset, and it is loaded with the

(a) Post-indexed addressing with writeback

(b) Pre-indexed addressing with writeback

Figure 3.4 ARM memory addressing modes involving writeback.

value 25. The instruction

## LDR R1,[R2],R10,LSL #2

can then be used in a program loop that loads register R1 with successive elements of the first row of the matrix on successive passes through the loop. Let us examine how this works, step by step. The first time that the Load instruction is executed, the effective address is [R2] = 1000. Therefore, the number 6, at this address, is loaded into R1. Then, the writeback operation changes the contents of R2 from 1000 to 1100 so that it points to the second number, -17. It does this by shifting the contents, 25, of

the offset register R10 left by two bit positions and then adding them to the contents of R2. The contents of R10 are not changed in this process. The left shift is equivalent to multiplying 25 by 4, generating the required offset 100. After this offset is added to the contents of R2, the new address 1100 is written back into R2. When the Load instruction is executed on the second pass through the loop, the second number, -17, is loaded into R1. The third number, 321, is loaded into R1 on the third pass, and so on.

This example involved adding the shifted contents of the offset register to the contents of the base register. As indicated in Table 3.1, the shifted offset can also be subtracted from the contents of the base register. Any shift distance in the range 0 through 31 can be selected, and either right or left shifting can be specified.

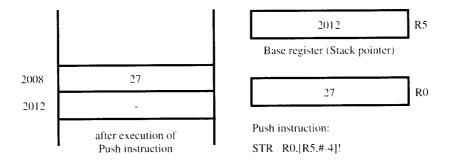

Figure 3.4b shows an example of pushing the contents, 27, of register R0 onto a stack. Register R5 is used as the stack pointer. Initially, it contains the address 2012 of the current TOS (top-of-stack) element. The Pre-indexed addressing mode with writeback, using an immediate offset, can be used to perform the Push operation with the instruction

The immediate offset -4 is added to the contents, 2012, of R5 and written back into R5. This new TOS location, 2008, is used as the effective address for the Store operation. The contents, 27, of register R0 are stored at location 2008.

#### **Load/Store Multiple Operands**

In addition to the Load and Store instructions for single operands, there are two instructions for loading and storing multiple operands. They are called Block transfer instructions. Any subset of the general purpose registers can be loaded or stored. Only word operands are allowed, and the OP codes used are LDM (Load Multiple) and STM (Store Multiple). The memory operands must be in successive word locations. All of the forms of pre- and post-indexing with and without writeback are available. They operate on a Base register Rn specified in the instruction. The offset magnitude is always 4 in these instructions so it does not have to be specified explicitly in the instruction. The list of registers must appear in increasing order in the assembly language expression for the instruction. As an example, assume that register R10 is the Base register and that it contains the value 1000 initially. Then, the instruction

transfers the words from locations 1000, 1004, 1008, and 1012 into registers R0, R1, R6, and R7, leaving the address value 1016 in R10 after the last transfer. The suffix IA in the OP code indicates "Increment After," corresponding to post-indexing. We will discuss the Load/Store Multiple instructions further in Section 3.6 in conjunction with implementing subroutines, where they are used to save and restore registers on a stack in an efficient way.

#### 3.1.3 REGISTER MOVE INSTRUCTIONS

It is often necessary to copy the contents of one register into another register or to load an immediate value into a register. The Move instruction

MOV Rd.Rm

uses the format shown in Figure 3.2 to copy the contents of register Rm into register Rd. An immediate operand in the low-order 8 bits of the instruction can also be loaded into register Rd by the Move instruction. For example,

MOV R0,#76

places the immediate value 76 into register R0. In both forms of the Move instruction, the source operand can be shifted before being placed in the destination register.

## 3.2 ARITHMETIC AND LOGIC INSTRUCTIONS

The ARM instruction set has a number of instructions for arithmetic and logic operations on operands that are either contained in the general-purpose registers or given as immediate operands in the instruction itself. Memory operands are not allowed for these instructions. There are instructions for different forms of addition and subtraction, and there are two instructions for multiplication. There are instructions for the AND, OR, NOT, XOR, and Bit-Clear logic operations. Instructions such as Compare are provided to set condition code flags based on the results from arithmetic or logic operations on two operands. They do not store the actual results in a register. The format for most of these instructions is shown in Figure 3.2.

#### 3.2.1 ARITHMETIC INSTRUCTIONS

The basic assembly language expression for arithmetic instructions is

OPcode Rd,Rn,Rm

where the operation specified by the OP code is performed using the operands in general-purpose registers Rn and Rm. The result is placed in register Rd. For example, the instruction

ADD R0,R2,R4

performs the operation

$R0 \leftarrow [R2] + [R4]$

and the instruction

SUB R0,R6,R5

performs the operation

$$R0 \leftarrow [R6] - [R5]$$

Instead of being contained in register Rm, the second operand can be given in the Immediate mode. Thus,

performs the operation

$$R0 \leftarrow [R3] + 17$$

The immediate value is contained in the 8-bit field in bits  $b_{7-0}$  of the instruction.

The second operand can be shifted or rotated before being used in the operation. When a shift or rotation is required, it is specified last in the assembly language expression for the instruction. The instruction

operates as follows: The second operand, which is contained in register R5, is shifted left 4 bit positions (equivalent to  $[R5] \times 16$ ), and it is then added to the contents of register R1; the sum is placed in register R0.

Two versions of a Multiply instruction are provided. The first version multiplies the contents of two registers and places the low-order 32-bits of the product in a third register. The high-order bits of the product, if there are any, are discarded. For example, the instruction

performs the operation

$$R0 \leftarrow [R1] \times [R2]$$

The second version specifies a fourth register whose contents are added to the product before storing the result in the destination register. Hence, the instruction

performs the operation

$$R0 \leftarrow [R1] \times [R2] + [R3]$$

This is called a Multiply-Accumulate operation. It is often used in numerical algorithms for digital signal processing. We will see an example of this type of application in Section 3.7. The fourth register is encoded in the Other information field of Figure 3.2. There are no provisions made for shifting or rotating any of the operands before they are used in the two Multiply instructions. Some versions of the ARM ISA accommodate double-length products (64 bits). (See Chapter 11.)

#### **Operand Shift Operations**

We noted earlier that one of the distinctive features of the ARM instruction set is that all instructions are executed conditionally. Another distinctive feature is the shifting and rotation operations that are incorporated into most instructions. In most other computer instruction sets, shifting operations are done using separate instructions. This is the case for the Motorola 68000 and the Intel IA-32 processors described in Parts II and III of this chapter. By incorporating shifting and rotation operations into instructions, as needed, the ARM architecture saves code space and can potentially improve execution time performance relative to more conventional processor designs. This feature is implemented using a *barrel shifter* circuit in the data path between the registers and the arithmetic and logic unit in the processor. Details of the shifting and rotation operations available, and their encoding in the instruction format, are given in Appendix B.

## 3.2.2 LOGIC INSTRUCTIONS

The logic operations AND, OR, XOR, and Bit-Clear are implemented by instructions with the OP codes AND, ORR, EOR, and BIC. They have the same format as the arithmetic instructions. The instruction

AND Rd.Rn.Rm

performs the operation

$Rd \leftarrow [Rn] \wedge [Rm]$

which is a bitwise logical AND between the operands in registers Rn and Rm. For example, if register R0 contains the hexadecimal pattern 02FA62CA and R1 contains the pattern 0000FFFF, then the instruction

AND R0,R0,R1

will result in the pattern 000062CA being placed in register R0.

The Bit-Clear instruction (BIC) is closely related to the AND instruction. It complements each bit in operand Rm before ANDing them with the bits in register Rn. Using the same R0 and R1 bit patterns as in the above example, the instruction

BIC R0,R0,R1

results in the pattern 02FA0000 being placed in R0.

The Move Negative instruction, with the OP-code mnemonic MVN, complements the bits of the source operand and places the result in Rd. If the contents of R3 are the hexadecimal pattern 0F0F0F0F, then the instruction

MVN R0,R3

places the result F0F0F0F0 in register R0.

| LDR<br>LDRB<br>LDRB<br>AND<br>ORR<br>STRB | R0.POINTER<br>R1.[R0]<br>R2.[R0.#1]<br>R2.R2.#&F<br>R2.R2.R1.LSL #4<br>R2.PACKED | Load address LOC into R0. Load ASCII characters into R1 and R2. Clear high-order 28 bits of R2. Or [R1] shifted left into [R2]. Store packed BCD digits |

|-------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           |                                                                                  | into PACKED.                                                                                                                                            |

Figure 3.5 An ARM program for packing two 4-bit decimal digits into a byte.

#### **Digit-Packing Program**

Figure 3.5 shows an ARM program for packing two 4-bit decimal digits into a memory byte location. The generic version of this program is shown in Figure 2.31 and is described in Section 2.10.2. The decimal digits, represented in ASCII code, are stored in byte locations LOC and LOC  $\pm$  1. The program packs the corresponding 4-bit BCD codes into a single byte location PACKED.

The first Load instruction in the program in Figure 3.5 assumes that the address LOC is stored in memory at address POINTER. As we will see in Section 3.4, an assembler directive can be used to place LOC in POINTER. This method of loading the address LOC into R0 is needed because a 32-bit address cannot be included as an immediate operand in an instruction. Location POINTER points to the BCD digit characters stored in successive byte locations. The two ASCII characters containing the BCD digits in their low-order four bits are loaded into the low-order byte positions of registers R1 and R2 by the next two Load instructions. The And instruction clears the high-order 28 bits of R2 to zero, leaving the second BCD digit in the four low-order bit positions. The Or instruction then shifts the first BCD digit in R1 to the left four positions and places it to the left of the second BCD digit in R2. The packed digits in the low-order byte of R2 are then stored into PACKED.

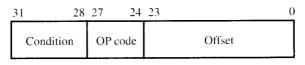

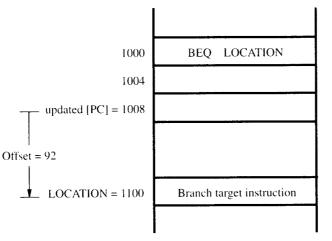

## **3.3** Branch Instructions

Conditional branch instructions contain a signed, 2's-complement, 24-bit offset that is added to the updated contents of the Program Counter to generate the branch target address. The format for the branch instructions is shown in Figure 3.6a, and an example is given in Figure 3.6b. The BEQ instruction (Branch if Equal to 0) causes a branch if the Z flag is set to 1.

The condition to be tested to determine whether or not branching should take place is specified in the high-order 4 bits,  $b_{31-28}$ , of the instruction word. A Branch instruction is executed in the same way as any other ARM instruction, that is, it is executed only if the current state of the condition code flags corresponds to the condition specified in the Condition field of the instruction.

(a) Instruction format

(b) Determination of a branch target address

Figure 3.6 ARM branch instructions.

At the time that the branch target address is computed, the contents of the PC have been updated to contain the address of the instruction that is two words beyond the Branch instruction itself. If the Branch instruction is at address location 1000, and the branch target address is 1100, as shown in Figure 3.6b, then the offset has to be 92 because the contents of the updated PC will be 1000 + 8 = 1008 when address 1100 is computed.

## **3.3.1 SETTING CONDITION CODES**

Some instructions, such as Compare, given by

CMP Rn,Rm

which performs the operation

$$[Rn] - [Rm]$$

have the sole purpose of setting the condition code flags based on the result of the subtraction operation. On the other hand, the arithmetic and logic instructions affect the condition code flags only if explicitly specified to do so by a bit in the OP-code

| STR R0.SUM Store sum. | LOOP | LDR<br>LDR<br>MOV<br>LDR<br>ADD<br>SUBS<br>BGT<br>STR | R1.N<br>R2.POINTER<br>R0.#0<br>R3.[R2].#4<br>R0.R0.R3<br>R1.R1.#1<br>LOOP<br>R0.SUM | Load count into R1. Load address NUM1 into R2. Clear accumulator R0. Load next number into R3. Add number into R0. Decrement loop counter R1. Branch back if not done. Store sum. |

|-----------------------|------|-------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|------|-------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 3.7 An ARM program for adding numbers.

field. This is indicated by appending the suffix S to the assembly language OP-code mnemonic. For example, the instruction

ADDS R0,R1,R2

sets the condition code flags, but

ADD R0,R1,R2

does not.

## 3.3.2 A LOOP PROGRAM FOR ADDING NUMBERS

Figure 3.7 shows a loop program for adding a list of numbers, patterned after the program in Figure 2.16. The load and store operations performed by the first, second, and last instructions use the Relative addressing mode. This assumes that the memory locations N, POINTER, and SUM are within the range reachable by the offset relative to the PC. Memory location POINTER contains the address NUM1 of the first of the numbers to be added, N contains the number of entries in the list, and SUM is used to store the sum. The Post-indexed addressing mode with writeback in the first instruction of the loop mirrors the use of the Autoincrement addressing mode in Figure 2.16.

## 3.4 ASSEMBLY LANGUAGE

The ARM assembly language has assembler directives to reserve storage space, assign numerical values to address labels and constant symbols, define where program and data blocks are to be placed in memory, and specify the end of the source program text. These facilities were described in general in Section 2.6.1.

We illustrate some of the ARM directives in Figure 3.8, which gives a complete source program for the program of Figure 3.7. The AREA directive, which uses the argument CODE or DATA, indicates the beginning of a block of memory that contains

|                                               | Memory<br>address<br>label  | Operation                                             | Addressing<br>or data<br>information                                                |

|-----------------------------------------------|-----------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------|

| Assembler directives                          |                             | AREA<br>ENTRY                                         | CODE                                                                                |

| Statements that generate machine instructions | LOOP                        | LDR<br>LDR<br>MOV<br>LDR<br>ADD<br>SUBS<br>BGT<br>STR | R1.N<br>R2.POINTER<br>R0.#0<br>R3.[R2].#4<br>R0.R0.R3<br>R1.R1.#1<br>LOOP<br>R0.SUM |

| Assembler directives                          | SUM<br>N<br>POINTER<br>NUM1 | AREA<br>DCD<br>DCD<br>DCD<br>DCD<br>END               | DATA<br>0<br>5<br>NUMH<br>317.2712.322                                              |

**Figure 3.8** ARM assembly language source program for the program in Figure 3.7.

either program instructions or data. The AREA directive actually requires more parameters to be specified, but they are not relevant for the level of discussion here. The ENTRY directive specifies that program execution is to begin at the following LDR instruction.

In the data area, which follows the code area, the DCD directives are used to label and initialize the data operands. The word locations SUM and N are initialized to 0 and 5, respectively, by the first two DCD directives. The address NUM1 is placed in the pointer location POINTER by the next DCD directive. The last DCD directive specifies that the five numbers to be added are placed in successive memory locations, starting at NUM1.

Constants in hexadecimal notation have a & prefix, and constants in base n, for n between two and nine, are denoted as n\_xxx. For example, 2\_101100 denotes a binary constant. Base ten constants do not need a prefix.

An EQU directive can be used to define symbolic names for constants. For example, the statement

TEN EQU 10

allows TEN to be used in a program instead of the decimal constant 10. When a number of registers are used in a program, it is convenient to use symbolic names for them that relate to their usage. The RN directive is used for this purpose. For example,

#### COUNTER RN 3

establishes the name COUNTER for register R3. The register names R0 to R15, PC (for R15), and LR (for R14) are predefined by the assembler.

#### 3.4.1 PSEUDO-INSTRUCTIONS

An alternative way of loading the address NUM1 into register R2 in Figure 3.8 is also provided in the assembly language. The *pseudo-instruction*

#### ADR Rd, ADDRESS

loads the 32-bit value ADDRESS into Rd. This instruction is not an actual machine instruction. The assembler chooses appropriate real machine instructions to implement pseudo-instructions. For example, the combination of the machine instruction

#### LDR R2,POINTER

and the data declaration directive

#### POINTER DCD NUM1

that is used in Figure 3.8 is one way to implement the pseudo-instruction

## ADR R2,NUM1

which would be placed at the position of the LDR instruction in the program. In this case, the assembler would need to allocate an appropriate data area for the DCD declaration.

A more efficient way to implement the ADR instruction is possible in this particular example, and it is the one that would be chosen by the assembler. When the address value to be loaded by the ADR instruction is within 255 bytes of the current contents of the PC (R15), the instruction

#### ADD Rd,R15,#offset

can be used to implement the ADR pseudo-instruction. If this is done in the example program, the location POINTER is not needed. The assembler implements the ADR pseudo-instruction with the real machine instruction

#### ADD R2.R15.#28

because NUM1 is 28 bytes beyond the updated PC when the ADD instruction is executed. This assumes that the data area immediately follows the STR instruction. This is not actually true because an instruction to return control to the operating system must follow the STR instruction, but it has been omitted.

## 3.5 I/O OPERATIONS

The ARM architecture uses memory-mapped I/O as described in Section 2.7. Reading a character from a keyboard or sending a character to a display can be done using program-controlled I/O as described in that section.

Suppose that bit 3 in each of the device status registers INSTATUS (keyboard) and OUTSTATUS (display) contains the respective control flags SIN and SOUT. Also assume that the keyboard DATAIN and display DATAOUT registers are located at addresses INSTATUS + 4 and OUTSTATUS + 4, immediately following the status register locations. The read and write wait loops can then be implemented as follows. Assume that address INSTATUS has been loaded into register R1. The instruction sequence

READWAIT LDR R3.[R1]

TST R3.#8

BEQ READWAIT

LDRB R3.[R1,#4]

reads a character into register R3 when a key has been pressed on the keyboard. The test (TST) instruction performs the bitwise logical AND operation on its two operands and sets the condition code flags based on the result. The immediate operand 8 has a single one in the bit 3 position. Therefore, the result of the TST operation will be zero if bit 3 of INSTATUS is zero and will be nonzero if bit 3 is one, signifying that a character is available in DATAIN. The BEQ instruction branches back to READWAIT if the result is zero, looping until a key is pressed, which sets bit 3 of INSTATUS to one.

Assuming that address OUTSTATUS has been loaded into register R2, the instruction sequence

WRITEWAIT LDR R4.[R2]

TST R4.#8

BEQ WRITEWAIT

STRB R3.[R2.#4]

sends the character in register R3 to the DATAOUT register when the display is ready to receive it.

These two routines can be used to read a line of characters from a keyboard, store them in the memory, and echo them back to a display, as shown in the program in Figure 3.9. This program is patterned after the generic program in Figure 2.20. Register R0 is assumed to contain the address of the first byte in the memory area where the line is to be stored. Registers R1 through R4 have the same usage as in the READWAIT and WRITEWAIT loops described above. The first Store instruction (STRB) stores the character read from the keyboard into the memory. The Post-indexed addressing mode with writeback is used in this instruction to step through the memory area, analogous to the use of the Autoincrement addressing mode in Figure 2.20. The Test if Equal (TEQ)

| READ | LDR<br>TST<br>BEQ<br>LDRB | R3.[R1]<br>R3.#8<br>READ<br>R3.[R1.#4] | Load [INSTATUS] and wait for character.  Read the character and          |

|------|---------------------------|----------------------------------------|--------------------------------------------------------------------------|

| ЕСНО | STRB<br>LDR<br>TST<br>BEQ | R3.[R0].#1<br>R4.[R2]<br>R4.#8<br>ECHO | store it in memory. Load [OUTSTATUS] and wait for display to be ready.   |

|      | STRB<br>TEQ<br>BNE        | R3.[R2.#4]<br>R3.#CR<br>READ           | Send character to display. If not carriage return, read more characters. |

Figure 3.9 An ARM program that reads a line of characters and displays it.

instruction tests whether or not the two operands are equal and sets the Z condition code flag accordingly.

#### **3.6** SUBROUTINES

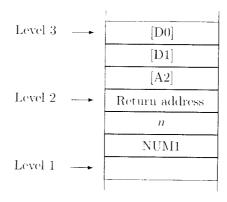

A Branch and Link (BL) instruction is used to call a subroutine. It operates in the same way as other branch instructions, with one added step. The return address, which is the address of the next instruction after the BL instruction, is loaded into register R14, which acts as a link register. Since subroutines may be nested, the contents of the link register must be saved on a stack by the subroutine. Register R13 is normally used as the pointer for this stack.

Figure 3.10 shows the program of Figure 3.7 rewritten as a subroutine. Parameters are passed through registers. The calling program passes the size of the number list and the address of the first number to the subroutine in registers R1 and R2; and the subroutine passes the sum back to the calling program in register R0. The subroutine also uses register R3. Therefore, its contents, along with the contents of the link register R14, are saved on the stack by the STMFD instruction. The suffix FD in this instruction specifies that the stack grows toward lower addresses and that the stack pointer R13 is to be predecremented before pushing words onto the stack. The LDMFD instruction restores the contents of register R3 and pops the saved return address into the PC (R15), performing the return operation automatically.

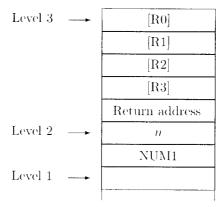

Figure 3.11*a* shows the program of Figure 3.7 rewritten as a subroutine with parameters passed on the stack. The parameters NUM1 and *n* are pushed onto the stack by the first four instructions of the calling program. We assume that NUM1 is contained in memory location POINTER. Registers R0 to R3 serve the same purpose inside the subroutine as in Figure 3.7. Their contents are saved on the stack by the first instruction of the subroutine along with the return address in R14. The contents of the stack at

| Calling pr | ogram                   |                                         |                                                                             |

|------------|-------------------------|-----------------------------------------|-----------------------------------------------------------------------------|

|            | LDR<br>LDR<br>BL<br>STR | R1.N<br>R2.POINTER<br>LISTADD<br>R0.SUM |                                                                             |

| Subroutin  | ıe                      |                                         |                                                                             |

| LISTADD    | STMFD                   | R13!.{R3.R14}                           | Save R3 and return address in R14 on stack, using R13 as the stack pointer. |

|            | MOV                     | R0.#0                                   |                                                                             |

| LOOP       | LDR                     | R3.[R2].#4                              |                                                                             |

|            | ADD                     | R0.R0.R3                                |                                                                             |

|            | SUBS                    | R1.R1.#1                                |                                                                             |

|            | BGT                     | LOOP                                    |                                                                             |

|            | LDMFD                   | R13!.{R3.R15}                           | Restore R3 and load return address into PC (R15).                           |

|            |                         |                                         |                                                                             |

**Figure 3.10** Program of Figure 3.7 written as an ARM subroutine; parameters passed through registers.

various times are shown in Figure 3.11b. After the parameters have been pushed and the Call instruction (BL) has been executed, the top of the stack is at level 2. It is at level 3 after all registers have been saved by the first instruction of the subroutine. The next two instructions load the parameters into registers R1 and R2 using offsets of 20 and 24 bytes into the stack, which reach to n and NUM1, respectively, from level 3. When the sum has been accumulated in R0, it is inserted into the stack by the Store instruction (STR), overwriting NUM1.

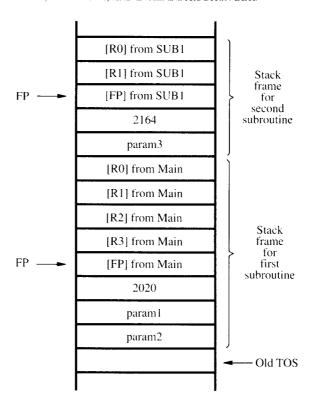

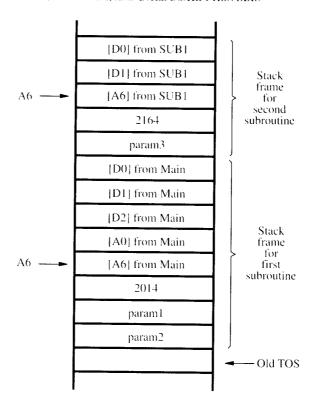

The last example of subroutines is the case of handling nested calls. Figure 3.12 shows the ARM code for the program of Figure 2.28. The stack frames corresponding to the first and second subroutines are shown in Figure 3.13. Register R12 is used as the frame pointer. Symbolic names are used for some of the registers in this example to aid program readability. Registers R12 (frame pointer), R13 (stack pointer), R14 (link register), and R15 (program counter), are labeled as FP, SP, LR, and PC, respectively. The assembler directive RN can be used to define these names.

The structure of the calling program and the subroutines is the same as in Figure 2.28. Aspects that are specific to ARM are as follows. Both the return address and the old contents of the frame pointer are saved on the stack by the first instruction in each subroutine. The second instruction sets the frame pointer to point to its saved value, as shown in Figure 3.13. This is consistent with the frame pointer position in Figures 2.27 and 2.29. The parameters are then referenced at offsets of 8, 12, and so on, as usual.

(Assume top of stack is at level 1 below.) Calling program R0.POINTERLDR Push NUM1 STRR0.[R13.#-4]!on stack. LDR R0.NPush n $R0.[R13,\#\!-\!4]!$ STRon stack. BLLISTADD R0.[R13.#4]LDR Move the sum into STR R0.SUM memory location SUM. ADD R13.R13.#8Remove parameters from stack. Subroutine LISTADD STMFD R13!.{R0-R3.R14} Save registers. LDR R1.[R13.#20] Load parameters LDR R2.[R13.#24]from stack. MOV R0.#0 LOOP LDR R3.[R2].#4 ADD R0.R0.R3 **SUBS** R1.R1.#1 BGT LOOP R0.[R13.#24]STRPlace sum on stack. LDMFD R13!.{R0-R3.R15} Restore registers and return.

## (a) Calling program and subroutine

(b) Top of stack at various times

**Figure 3.11** Program of Figure 3.7 written as an ARM subroutine; parameters passed on the stack.

| Memory<br>location |            | Instructions          | Comments                      |

|--------------------|------------|-----------------------|-------------------------------|

| Calling prog       | ram        |                       |                               |

|                    | :          |                       |                               |

| 2000               | LDR        | R10.PARAM2            | Place parameters on stack.    |

| 2004               | STR        | R10.[SP.#-4]!         |                               |

| 2008               | LDR        | R10.PARAM1            |                               |

| 2012               | STR        | R10.[SP.#-4]!         |                               |

| 2016               | BL         | SUB1                  |                               |

| 2020               | LDR        | R10.[SP]              | Store SUB1 result.            |

| 2024               | STR        | R10.RESULT            | D                             |

| 2028               | ADD        | SP.SP.#8              | Remove parameters from stack. |

| 2032               | next instr | HC(10)1               |                               |

|                    | :          |                       |                               |

| First subrou       | tine       |                       |                               |

| 2100 SUB1          | STMFD      | SP!.{R0-R3.FP.LR}     | Save registers.               |

| 2104               | ADD        | FP.SP.#16             | Load frame pointer.           |

| 2108               | LDR        | R0.[FP.#8]            | Load parameters.              |

| 2112               | LDR        | R1.[FP.#12]           |                               |

|                    | :          |                       |                               |

|                    | LDR        | R2.PARAM3             | Place parameter on stack.     |

|                    | STR        | R2.[SP.#-4]!          | That parameter on mack.       |

| 2160               | BL         | SUB2                  |                               |

| 2164               | LDR        | R2.[SP].#4            | Pop SUB2 result into R2.      |

| -                  |            | ř 1 m                 | •                             |

|                    | ;<br>CTD   | Do (DD #ol            | Dlago novalt on starls        |

|                    | STR        | R3.[FP.#8]            | Place result on stack.        |

|                    | LDMFD      | SP!.{R0-R3.FP.PC}     | Restore registers and return. |

| Second subroutine  |            |                       |                               |

| 3000 SUB2          | STMFD      | SP!.{R0.R1.FP.LR}     | Save registers.               |

| экки эк-192        | ADD        | FP.SP.#8              | Load frame pointer.           |

|                    | LDR        | R0.[FP.#8]            | Load parameter.               |

|                    |            | = [ = = - H]          | . 1                           |

|                    | (100.12)   | Tal [IDD 11:0]        | DI le colò                    |

|                    | STR        | R1.[FP.#8]            | Place result on stack.        |

|                    | LDMFD      | $SP!.\{R0.R1.FP.PC\}$ | Restore registers and return. |

|                    |            |                       |                               |

Figure 3.12 Nested subroutines in ARM assembly language.

Figure 3.13 ARM stack frames for Figure 3.12.

The last instruction in each subroutine restores the old value of the frame pointer as well as the values of the other registers used, and pops the return address from the stack into the PC.

## **3.7** PROGRAM EXAMPLES

In this section, we give ARM versions of the programs for dot product, byte sorting, and linked-list operations that were described in Chapter 2. The programs are patterned after the generic programs shown in Figures 2.33, 2.34, 2.37, and 2.38. We will describe only those aspects of the ARM code that differ from the generic versions used in Chapter 2.

## 3.7.1 VECTOR DOT PRODUCT PROGRAM

The first two instructions in Figure 3.14 load the addresses of the A and B vectors into registers R1 and R2. They are the ADR pseudo-instructions described in Section 3.4.1. If AVEC and BVEC are close enough to the program, an Add instruction using the current

|      | ADR  | R1.AVEC     | R1 points to vector A.                      |

|------|------|-------------|---------------------------------------------|

|      | ADR  | R2.BVEC     | R2 points to vector B.                      |

|      | LDR  | R3.N        | R3 is the loop counter.                     |

|      | MOV  | R0,#0       | R0 accumulates the dot product              |

| LOOP | LDR  | R4.[R1].#4  | Load A component.                           |

|      | LDR  | R5,[R2].#4  | Load B component.                           |

|      | MLA  | R0.R4.R5.R0 | Multiply components and accumulate into R0. |

|      | SUBS | R3.R3.#1    | Decrement the counter.                      |

|      | BNE  | LOOP        | Branch back if not done.                    |

|      | STR  | R0.DOTPROD  | Store dot product.                          |

Figure 3.14 An ARM dot-product program.

value of the PC can be used to generate the addresses. The Relative addressing mode is used to access the contents of N and DOTPROD, and the Post-indexed addressing mode with writeback is used in the first two instructions of the loop. The Multiply-Accumulate instruction (MLA) performs the necessary arithmetic operations. It multiplies the vector elements in R4 and R5 and accumulates their product into R0.

#### 3.7.2 BYTE-SORTING PROGRAM

Figure 3.15 shows the byte-sorting program. It follows the same structure as used in the program in Figure 2.34b. The address LIST of the first byte is loaded into register R4. It is used in the second to the last Compare instruction to determine when the inner loop (based on the k index) terminates. Correspondingly, R5 contains the address LIST  $\pm 1$  and is used in the last Compare instruction to determine when the outer loop (based on the j index) terminates. The base register R2 is used to step the j index backward from the end of the list in the outer loop. Register R3 steps the k index backward through each sublist in the inner loop. The Pre-indexed addressing mode with writeback is used to load LIST(j) bytes into register R0 and to load LIST(k) bytes into R1 in the outer and inner loops, respectively.

The conditional execution feature of the ARM instruction set is used to advantage in the inner loop when LIST(k) must be interchanged with LIST(j). The three-instruction sequence STR, STR, MOV is only executed if LIST(k) is greater than LIST(k), as indicated by the GT suffixes. The forward conditional branch to NEXT in the generic program in Figure 2.34k is not needed in the ARM program.

## 3.7.3 LINKED-LIST INSERTION AND DELETION SUBROUTINES

The insertion and deletion subroutine programs in Figures 3.16 and 3.17 mirror the structure of the corresponding programs in Figures 2.37 and 2.38 quite closely. The forward conditional branches used in the generic programs are not needed in the ARM

```

for (j = n-1; j > 0; j = j-1)

{ for (k = j-1; k >= 0; k = k-1)

{ if (LIST[k] > LIST[j])

{ TEMP = LIST[k];

LIST[k] = LIST[j];

LIST[j] = TEMP;

}

```

#### (a) C-language program for sorting

|       | ADR    | R4.LIST      | Load list pointer register R4.               |

|-------|--------|--------------|----------------------------------------------|

|       | LDR    | R10.N        | and initialize outer loop base               |

|       | ADD    | R2.R4.R10    | register R2 to LIST $+ n$ .                  |

|       | ADD    | R5.R4.#1     | Load LIST $+ 1$ into R5.                     |

| OUTER | LDRB   | R0.[R2.#-1]! | Load LIST $(j)$ into R0.                     |

|       | MOV    | R3.R2        | Initialize inner loop base register          |

|       |        |              | R3 to LIST $+ n - 1$ .                       |

| INNER | LDRB   | R1.[R3.#-1]! | Load LIST $(k)$ into R1.                     |

|       | CMP    | R1.R0        | Compare $LIST(k)$ to $LIST(j)$ .             |

|       | STRGTB | R1.[R2]      | If LIST $(k) > \text{LIST}(j)$ , interchange |

|       | STRGTB | R0.[R3]      | LIST(k) and $LIST(j)$ , and                  |

|       | MOVGT  | R0.R1        | move (new) LIST $(i)$ into R0.               |

|       | CMP    | R3.R4        | If $k > 0$ , repeat                          |

|       | BNE    | INNER        | inner loop.                                  |

|       | CMP    | R2.R5        | If $j > 1$ , repeat                          |

|       | BNE    | OUTER        | outer loop.                                  |

|       |        |              |                                              |

(b) ARM program implementation

Figure 3.15 An ARM byte-sorting program.

programs. This is a result of the use of conditional execution of instruction blocks, as done in the byte-sorting program in Figure 3.15. Parameters are passed through registers in both ARM subroutines.

Register mnemonics are used to reflect register usage, instead of the usual Ri notation. The assembler directive RN can be used to define the equivalences. As in the programs in Figures 2.37 and 2.38, RHEAD contains the address of the first record in

| CMP<br>MOVEQ<br>MOVEQ<br>LDR<br>LDR<br>CMP<br>STRGT<br>MOVGT | RHEAD.#0 RHEAD.RNEWREC PC.R14 R0.[RHEAD] R1.[RNEWREC] R0.R1 RHEAD.[RNEWREC.#4] RHEAD.RNEWREC | Check if list empty.  If empty, insert new record as head.  If not empty, check if new record becomes new head, and insert if yes.                                                                                                                                                                                                                           |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVGT MOV LDR CMP STREQ MOVEQ                                | PC.R14 RCURRENT.RHEAD RNEXT.[RCURRENT.#4] RNEXT.#0 RNEWREC.[RCURRENT.#4] PC.R14              | If new record goes after<br>current head,<br>find where.<br>New record becomes new tail.                                                                                                                                                                                                                                                                     |

| LDR<br>CMP<br>MOVLT                                          | R0.[RNEXT] R0.R1 RCURRENT.RNEXT                                                              | Go further? Yes, then loop back.                                                                                                                                                                                                                                                                                                                             |

| STR<br>STR<br>MOV                                            | RNEXT.[RNEWREC.#4]<br>RNEWREC.[RCURRENT.#4]<br>PC.R14                                        | Otherwise, insert new record between current and next records.                                                                                                                                                                                                                                                                                               |

|                                                              | MOVEQ MOVEQ LDR LDR CMP STRGT MOVGT MOVGT MOV LDR CMP STREQ MOVEQ LDR CMP MOVLT BLT STR STR  | MOVEQ RHEAD.RNEWREC  MOVEQ PC.R14  LDR R0.[RHEAD]  LDR R1.[RNEWREC]  CMP R0.R1  STRGT RHEAD.[RNEWREC.#4]  MOVGT RHEAD.RNEWREC  MOVGT PC.R14  MOV RCURRENT.RHEAD  LDR RNEXT.[RCURRENT.#4]  CMP RNEXT.#0  STREQ RNEWREC.[RCURRENT.#4]  MOVEQ PC.R14  LDR R0.[RNEXT]  CMP R0.R1  MOVLT RCURRENT.RNEXT  BLT LOOP  STR RNEXT.[RNEWREC.#4]  STR RNEXT.[RNEWREC.#4] |

Figure 3.16 An ARM subroutine for inserting a new record into a linked list.

| Subroutine |                |                            |                                            |

|------------|----------------|----------------------------|--------------------------------------------|

| DELETION   | LDR<br>CMP     | R0.[RHEAD]<br>R0.RIDNUM    | Check if record to be deleted is the head. |

|            | LDREQ<br>MOVEQ | RHEAD.[RHEAD.#4]<br>PC.R14 | If yes, delete and return.                 |

|            | MOV            | RCURRENT.RHEAD             | Otherwise, continue search.                |

| LOOP       | LDR            | RNEXT.[RCURRENT.#4]        | Is next record the one                     |

|            | LDR            | R0.[RNEXT]                 | to be deleted?                             |

|            | СМР            | R0.RIDNUM                  |                                            |

|            | LDREQ          | R0.[RNEXT.#4]              | If yes, delete                             |

|            | STREQ          | R0.[RCURRENT.#4]           | and return.                                |

|            | MOVEQ          | PC.R14                     |                                            |

|            | MOV            | RCURRENT.RNEXT             | Otherwise, loop back                       |

|            | В              | LOOP                       | to continue search.                        |

|            |                |                            |                                            |

Figure 3.17 An ARM subroutine for deleting a record from a linked list.

the list. RNEWREC contains the address of the new record to be inserted. RIDNUM contains the ID number of the record to be deleted. The two registers RCURRENT and RNEXT contain link addresses that are used by the subroutines to walk through the list to find the insertion or deletion positions.

The insertion subroutine in Figure 3.16, patterned after the subroutine in Figure 2.37, has the following structure. The first three instructions insert the new record as the head (and tail) of a previously empty list. Recall that the new record is assumed to initially have zero in its link field. The third instruction in this block performs the return operation from the subroutine to the calling program. The next six instructions determine whether or not the new record should become the new head of the existing list. The list is ordered by increasing ID numbers. Therefore, if the ID number in the first word of the current head record is greater than the ID number of the new record, then the new record becomes the new head of the list. The conditionally executed STRGT and MOVGT instructions perform the appropriate link address operations if this is the case. Otherwise, the remaining part of the subroutine determines where the new record should be inserted in the list after the current head, including the possibility that the new record becomes the tail.

The deletion subroutine is shown in Figure 3.17. If the record to be deleted is the head of the list, the first four instructions discover this, delete it, and return. Otherwise, the remainder of the subroutine uses registers RCURRENT and RNEXT to move through the list looking for the record. The LDREQ/STREQ pair of instructions delete the record when it is found to be the one pointed to by RNEXT.

As with the generic programs in Figures 2.37 and 2.38, the insertion subroutine in Figure 3.16 assumes that the ID number of the new record does not match that of any record already in the list, and the deletion subroutine in Figure 3.17 assumes that there exists a record in the list with an ID number that does match the contents of RIDNUM. Problems 3.23 and 3.24 consider how the subroutines should be changed to signal an error if the assumptions are not true.

#### PART II

#### THE 68000 EXAMPLE

In this second part of Chapter 3, we describe the basic architecture of processors in Motorola's 680X0 family by discussing the 68000 ISA. The family includes several processors that provide different performance levels. All members of the family have the same basic architecture, but later members have additional features that enhance their performance. We use the 68000 here because it is somewhat simpler to describe, yet it portrays the salient features of the entire family. We do not provide a comprehensive description of the 68000. For such information, the reader can consult manufacturer's information [6]. Instead, we concentrate on the most important aspects of the 68000, giving sufficient detail to enable the reader to prepare, assemble, and run simple programs. The distinguishing features of various members of the 680X0 family, as well as some of the features introduced for performance enhancement, are described in Chapter 11. The programs from Chapter 2 are presented here in the 68000 assembly language to illustrate various aspects of the 68000 architecture.

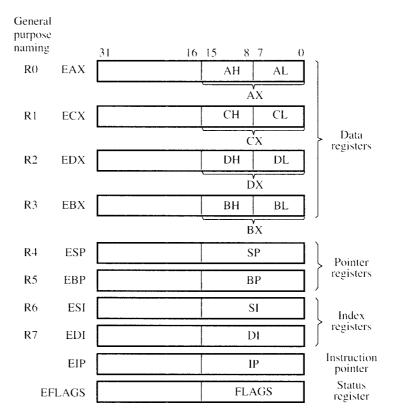

#### 3.8 REGISTERS AND ADDRESSING

The 68000 processor is characterized by a 16-bit external word length because the processor chip has 16 data pins for connection to the memory. However, data are manipulated inside the processor in registers that contain 32 bits. The more advanced models of this family are the 68020, 68030, and 68040 processors, which come in larger chip packages and have 32 external data pins. Thus, they can deal with data both internally and externally in 32-bit quantities. Tabak [7] covers these members of the 680X0 family, emphasizing the 68040.

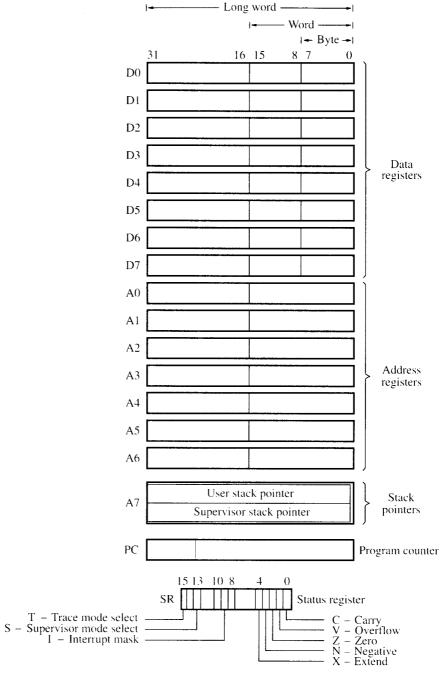

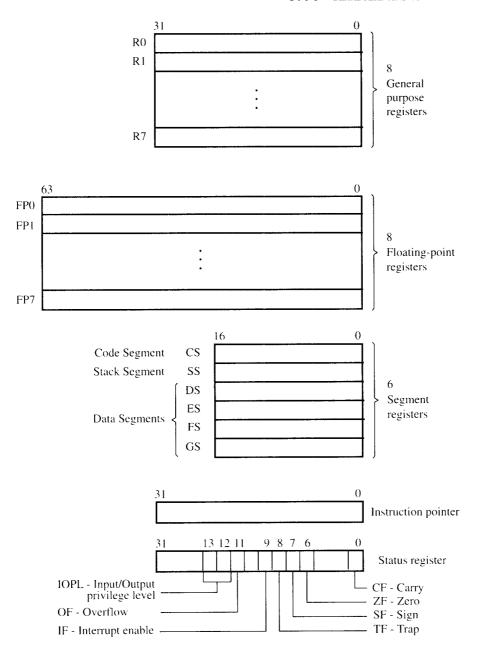

#### 3.8.1 THE 68000 REGISTER STRUCTURE

The 68000 register structure, shown in Figure 3.18, has 8 data registers and 8 address registers, each 32 bits long. The data registers serve as general-purpose accumulators and as counters.

The 68000 instructions deal with operands of three different lengths. A 32-bit operand is said to occupy a *long word*, a 16-bit operand constitutes a word, and an 8-bit operand is a byte. When an instruction uses a byte or a word operand in a register, the operand is in the low-order bit positions of the register. In most cases, such instructions do not affect the remaining high-order bits of the register, but some instructions extend the sign of a shorter operand into the high-order bits.

The address registers hold information used in determining the addresses of memory operands. This information may be given in either long word or word sizes. When the address of a given memory location is in an address register, the register serves as a pointer to that location. Both address and data registers can also be used as index registers. One address register, A7, has the special function of being the processor stack pointer. The role of this register is discussed in Section 3.13.

The address registers and address calculations involve 32 bits. However, in the 68000, only the least-significant 24 bits of an address are used externally to access the memory. The 68020, 68030, and 68040 processors have 32 external address lines as well as 32 data lines.

The last register shown in Figure 3.18 is the processor *status register*, SR. It contains five condition code bits, which are described in Section 3.11.1; three interrupt bits, which are discussed in Chapter 4; and two mode-select bits, which are explained in Section 3.13.

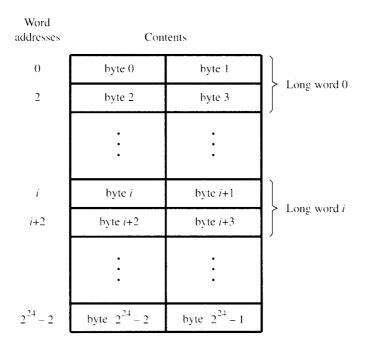

## 3.8.2 ADDRESSING

The memory of a 68000 computer is organized in 16-bit words and is byte addressable. Two consecutive words can be interpreted as a single 32-bit long word. Memory addresses are assigned as shown in Figure 3.19. A word must be aligned on an even boundary, that is, its address must be an even number. The big-endian address assignment is used. The byte in the high-order position of a word has the same address as the word, whereas the byte in the low-order position has the next higher address.

Figure 3.18 The 68000 register structure.

Figure 3.19 Map of addressable locations in the 68000.

Since the 68000 generates 24-bit addresses, its addressable space is  $2^{24}$  (16,777,216 or 16M) bytes. This addressable space may be thought of as consisting of 512 ( $2^9$ ) *pages* of 32K ( $2^{15}$ ) bytes each. Thus, hexadecimal addresses 0 to 7FFF constitute page 0, addresses 8000 to FFFF make up page 2, and so on. The last page consists of addresses FF8000 to FFFFFF.

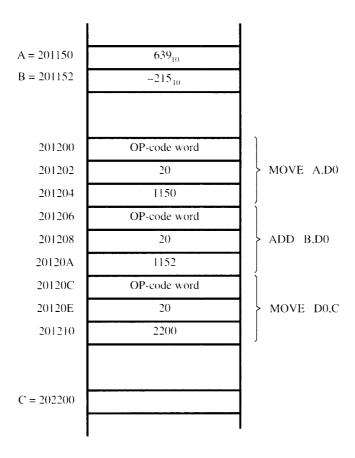

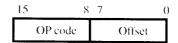

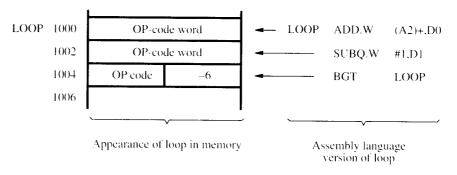

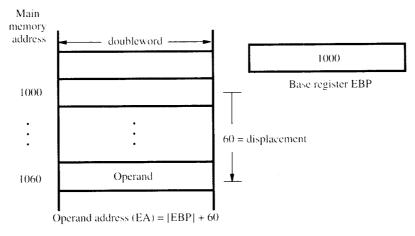

The 68000 has several addressing modes, including those discussed in Section 2.5. Many of the 68000's instructions fit into a 16-bit word, but some require additional words for extra addressing information. The first word of an instruction is the OP-code word, which specifies the operation to be performed and gives some addressing information. The rest of the addressing information, if any, is given in subsequent words. The available addressing modes are defined as follows:

Immediate mode — The operand is contained in the instruction. Four sizes of operands can be specified. Byte, word, and long-word operands are given following the OP-code word. The fourth size consists of very small numbers that can be included directly in the OP-code word of some instructions.

Absolute mode — The absolute address of an operand is given in the instruction, following the OP code. There are two versions of this mode — long and short. In the long mode, a 24-bit address is specified explicitly. In the short mode, a 16-bit value is given in the instruction to be used as the low-order 16 bits of an address. The sign bit of this value is extended to provide the high-order eight bits of the address. Since the sign bit is either 0 or 1, it follows that in the short

mode only two pages of the addressable space can be accessed. These are the 0 page and the FF8 page, each containing 32K bytes.

*Register mode* — The operand is in a processor register specified in the instruction.

Register indirect mode — The effective address of the operand is in an address register specified in the instruction.

Autoincrement mode — The effective address of the operand is in an address register, An, specified in the instruction. After the operand is accessed, the contents of An are incremented by 1, 2, or 4, depending on whether a byte, a word, or a long-word operand, respectively, is involved.

Autodecrement mode — The contents of an address register, An, specified in the instruction are decremented by 1, 2, or 4, depending on whether a byte, a word, or a long-word operand, respectively, is involved. The effective address of the operand is the decremented contents of An.

Basic index mode — A 16-bit signed offset and an address register, An, are specified in the instruction. The sum of this offset and the contents of An is the effective address of the operand.

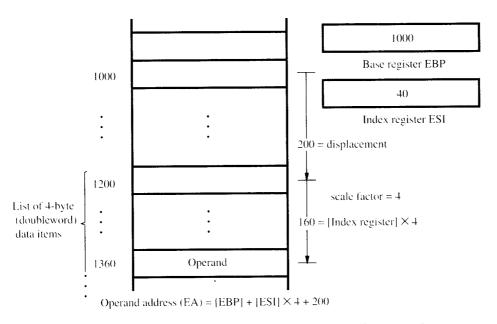

Full index mode — An 8-bit signed offset, an address register An, and an index register Rk (either an address or a data register) are given in the instruction. The effective address of the operand is the sum of the offset and the contents of registers An and Rk. Either all 32 bits or the sign-extended low-order 16 bits of Rk are used in the derivation of the address.

Basic relative mode — This is the same mode as the basic index mode except that the program counter is used instead of an address register, An.

Full relative mode — This is the same mode as the full index mode except that the program counter is used instead of an address register, An.

The addressing modes and their assembler syntax are summarized in Table 3.2.

Note that there are two versions of the index mode. The basic index mode corresponds to the mode depicted in Figure 2.13. The full index mode involves the contents of two registers and an offset constant given in the instruction. The size of the offset constant is 16 bits in the basic mode and 8 bits in the full mode.

In the full index mode, the second register, Rk, can be used in two ways: either all 32 bits are used or only the low-order 16 bits are used. The two possibilities are indicated to the assembler by appending a size indicator — L for a long word or W for a word — to the name of the register, for example, D1.L or D1.W. The latter is the default size if no indicator is given. When a 16-bit word is used in the computation of a 32-bit effective address, this word is sign extended.

In either of the two index modes, the program counter may be used in place of the address register. The resulting addressing modes are called the relative modes because the effective address is specified in terms of the distance between the operand and the instruction that refers to it. Consider the instruction

Table 3.2 68000 addressing modes

| Name              | Assembler syntax                 | Addressing function                      |

|-------------------|----------------------------------|------------------------------------------|

| Immediate         | #Value                           | Operand = Value                          |

| Absolute Short    | Value                            | EA = Sign Extended WValue                |

| Absolute Long     | Value                            | EA = Value                               |

| Register          | Rn                               | $EA = R_n$<br>that is, Operand = $[R_n]$ |

| Register Indirect | (An)                             | $\mathbf{E}\mathbf{A} = [\mathbf{A}_n]$  |

| Autoincrement     | (An)+                            | $EA = [A_n];$<br>Increment $A_n$         |

| Autodecrement     | -(An)                            | Decrement $A_n$ :<br>EA = $[A_n]$        |

| Indexed basic     | WValue(An)                       | $EA = WValue + [A_n]$                    |

| Indexed full      | BValue(An,Rk.S)                  | $EA = BValue + [A_n] + [R_k]$            |

| Relative basic    | WValue(PC)<br>or Label           | EA = WValue + [PC]                       |

| Relative full     | BValue(PC,Rk.S)<br>or Label (Rk) | $EA = BValue + [PC] + [R_k]$             |

|                   |                                  |                                          |

EA = effective address

Value = a number given either explicitly or represented by a label BValue = an 8-bit Value

BValue = an 8-bit Value WValue = a 16-bit Value A<sub>n</sub> = an address register

$R_n^m = an address or a data register$

a size indicator: W for sign-extended 16-bit word

and L for 32-bit long word

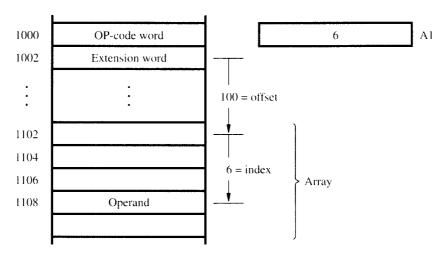

When encoded in machine form, this instruction consists of two words. The OP-code word specifies that this is an Add instruction, that the destination register is data register D0, and that the full relative addressing mode is used for the source operand. The second word, also called the *extension word*, specifies that register A1 is used as the index register and it contains the offset value 100 encoded in 8 bits.

Assume that the preceding instruction is stored in location 1000 and that register A1 contains the value 6, as shown in Figure 3.20. When the OP-code word of this instruction has been fetched and while it is being decoded by the processor, the program counter points to the extension word, which means that the program counter contains the value 1002. Therefore, the effective address of the source operand is

$$EA = [PC] + [A1] + 100$$

$$= 1002 + 6 + 100$$

$$= 1108$$

Figure 3.20 An example of 68000 full relative mode for the instruction ADD 100(PC,A1),D0.

Figure 3.20 suggests how this addressing mode can be used to access an entry in an array. The offset value specifies the distance between the first entry in the array and the instruction. Then the index register gives the distance between that point and the desired operand, which is the fourth word in the array.

We have written the relative mode in an explicit format. Most assemblers allow this mode to be specified in a simpler way. First, the assembler must be informed that relative addressing is to be used in a given section of the program through an appropriate assembler directive. Next, after the name ARRAY has been assigned the value 1102, the instruction in Figure 3.20 can be written as

## ADD ARRAY(A1),D0

The assembler interprets this specification of the source operand as being in the full relative mode, and it computes the offset as indicated in the figure. The assembler does not know, and does not need to know, what the contents of register A1 will be when the instruction is executed. For example, this instruction may be inside a program loop, in which case A1 could be used to access successive elements of the array.

The full relative mode is limited by the fact that the offset is a 2's-complement 8-bit number, thus restricting its values to the range -128 to +127 bytes.

#### **3.9** Instructions

The 68000 ISA provides an extensive set of instructions, most of which can operate on any of the three possible sizes of operands. The instruction set is summarized in Appendix C. All addressing modes can be used in a uniform way with most instructions. Instruction sets that exhibit this feature are said to be *orthogonal*.

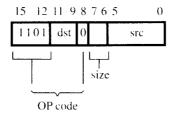

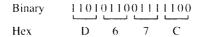

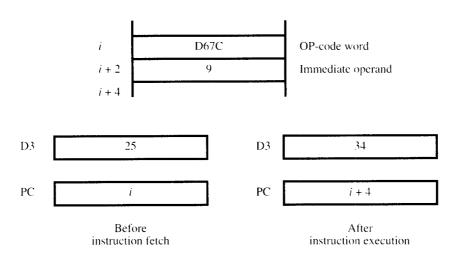

(a) Format of the OP-code word for an ADD instruction

(b) Encoding of the OP-code word

(c) Consequences of the execution

Figure 3.21 The 68000 instruction ADD #9,D3.

The 68000 has both one-operand and two-operand instructions. A two-operand instruction is written as

## OP src,dst

where the operation OP is performed using the source and destination operands. The result is placed in the destination location. An example is given in Figure 3.21, which

shows the instruction

This instruction performs the action

$$dst \leftarrow [src] + [dst]$$

which results in adding the value 9 to the contents of register D3 and storing the result back in D3.